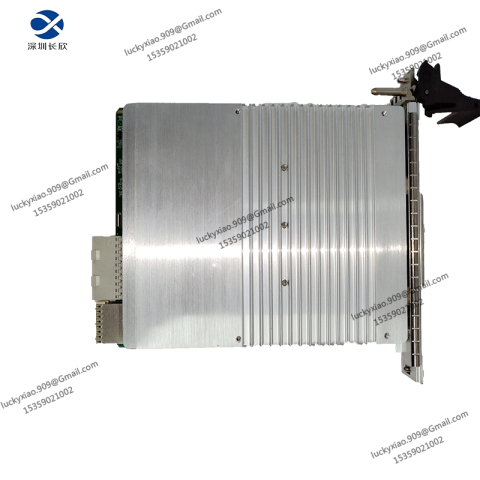

AMAT 0190-73524: Technical Specifications

- Component Type

- Category: Plasma Chamber Liner or Deposition Shield Kit

- Purpose: Protects chamber walls from plasma erosion and process byproduct accumulation during etch or deposition processes.

- Material: High-purity alumina (Al₂O₃), yttria (Y₂O₃), or silicon carbide (SiC) coatings for extreme chemical/thermal resistance.

- Physical Specifications

- Dimensions: Custom-fit for AMAT process chambers (e.g., diameter 400–500 mm for 300mm wafer tools).

- Thickness: 5–15 mm (multi-segment design for easy replacement).

- Weight: 8–15 kg (depending on chamber size and material).

- Operational Parameters

- Temperature Tolerance: Up to 600°C (continuous operation).

- Plasma Compatibility: Withstands high-density plasma (HDP) environments (e.g., RF power density ≤ 5 W/cm²).

- Chemical Resistance: Resists aggressive etchants (Cl₂, HBr, CF₄) and deposition precursors (WF₆, TEOS, NH₃).

- Integration & Compatibility

- Tool Platforms: Compatible with AMAT Centura® or Endura® etch/deposition systems.

- Interfaces: Pre-aligned mounting points for fast installation (<30 minutes downtime).

- Particle Control: Engineered surface finish (Ra ≤ 0.4 µm) to minimize particle generation.

- Certifications & Standards

- Complies with SEMI F47-0706 (particle shedding standards).

- REACH/RoHS compliant (no hazardous coatings).

- Lifetime & Maintenance

- Service Life: 3,000–5,000 process hours (dependent on plasma intensity).

- Cleaning: Dry plasma clean (e.g., O₂/NF₃) or wet chemical clean (dilute HF or IPA).

Functional Overview

The AMAT 0190-73524 is a consumable component critical to maintaining process consistency and chamber longevity in semiconductor manufacturing. Key functionalities include:

- Chamber Protection

- Shields metallic chamber walls from reactive plasma species, preventing contamination from metal sputtering.

- Reduces metallic contamination on wafers (<1 ppb levels), crucial for high-k/metal gate processes.

- Byproduct Management

- Traps and contains etch/deposition byproducts (e.g., polymers, metal halides), minimizing flaking and defect generation.

- Extends time between chamber wet cleans (up to 2x longer intervals).

- Process Uniformity

- Maintains consistent plasma impedance and gas flow dynamics, ensuring etch/deposition uniformity (e.g., <±2% thickness variation).

- Cost Efficiency

- Modular design allows replacement of individual liner segments instead of the entire kit, reducing consumable costs.

- Applications

- Etch Processes:

- Dielectric etch (SiO₂, Si₃N₄) for advanced logic nodes (3nm/2nm).

- High-aspect-ratio etch (HAR) for 3D NAND vertical channels.

- Deposition Processes:

- PECVD of low-k dielectrics or SiN spacer layers.

- ALD of ultrathin barriers (e.g., TaN, TiN).

- Etch Processes:

Critical Notes

- Safety: Handle with cleanroom protocols to avoid introducing particles; pre-bake liners before installation to outgas contaminants.

- Compatibility: Verify material compatibility with specific chemistries (e.g., Y₂O₃ for fluorine-based plasmas, Al₂O₃ for chlorine-based etches).

-480x480.png)

There are no reviews yet.