GE DS200UCPBG6AFB Key thyristor (SCR) module

GE DS200UCPBG6AFB Technical Specification

Specification

|

Attribute

|

Detail

|

|---|---|

|

Part Number

|

|

|

Manufacturer

|

General Electric (GE)

|

|

Series

|

Mark V Speedtronic™

|

|

Country of Origin

|

USA

|

|

Function

|

SCR Firing Control Board (Gas Turbine Starting)

|

Description

The GE DS200UCPBG6AFB is a critical thyristor (SCR) firing control module for GE’s Mark V gas turbine startup systems. It generates precision gate pulses to regulate excitation current for generator synchronization and soft-start sequencing. Integrates with DS200SLCCG load commutation boards and features FPGA-based waveform synthesis, closed-loop feedback, and fault diagnostics.

Features

- SCR Control: 6-pulse firing for 3-phase bridges (±0.1° timing accuracy).

- Adaptive Synchronization: Auto-phase matching (25–60 Hz) via PLL circuitry.

- Protection Circuits:

- dI/dt & dV/dt suppression for SCRs

- Overcurrent lockout (>150% nominal)

- Gate pulse loss detection

- Isolated Interfaces: Fiber-optic trigger outputs (6 channels), 4–20mA feedback.

- Legacy Compatibility: Direct replacement for DS200UCPAG1B/UCPBG1A.

- Diagnostic LEDs: Per-phase status, fault codes (OC, UV, OV, sync loss).

Electrical Specifications

|

Parameter

|

Specification

|

|---|---|

|

Input Voltage

|

125V DC (from Mark V rack)

|

|

Gate Drive Output

|

3.0A peak (2.0 µs pulse, 2 kV isolation)

|

|

Feedback Sensing

|

±10V analog (phase voltage/current)

|

|

Timing Resolution

|

0.01° (at 60 Hz)

|

|

Operating Temp

|

-30°C to +65°C

|

Product Properties

|

Property

|

Specification

|

|---|---|

|

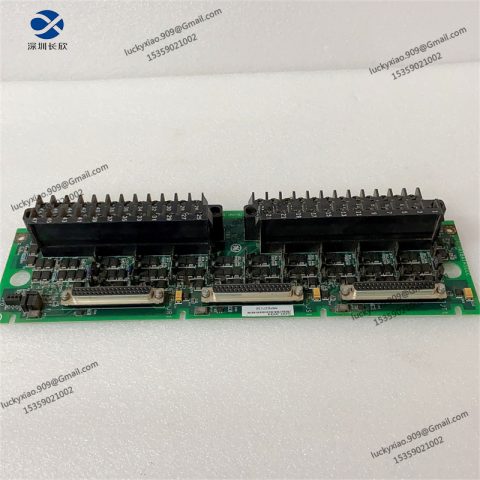

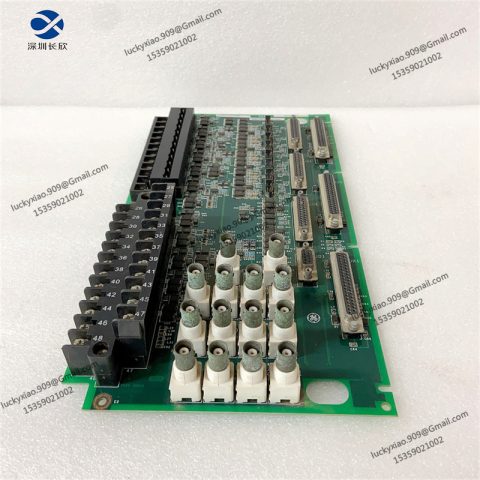

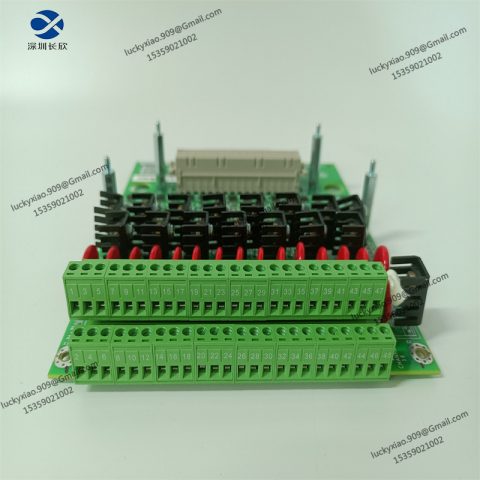

I/O Connectors

|

2× 36-pin AMPLIMITE (firing pulses)

1× 25-pin D-sub (control signals) |

|

Communication

|

RS-422 sync input (from DS200TCRAG)

|

|

FPGA

|

Xilinx XC3042 (firmware rev. G6AFB-01+)

|

|

MTBF

|

87,000 hours (Bellcore TR-332)

|

|

Compliance

|

UL 508, CSA C22.2 No. 142

|

|

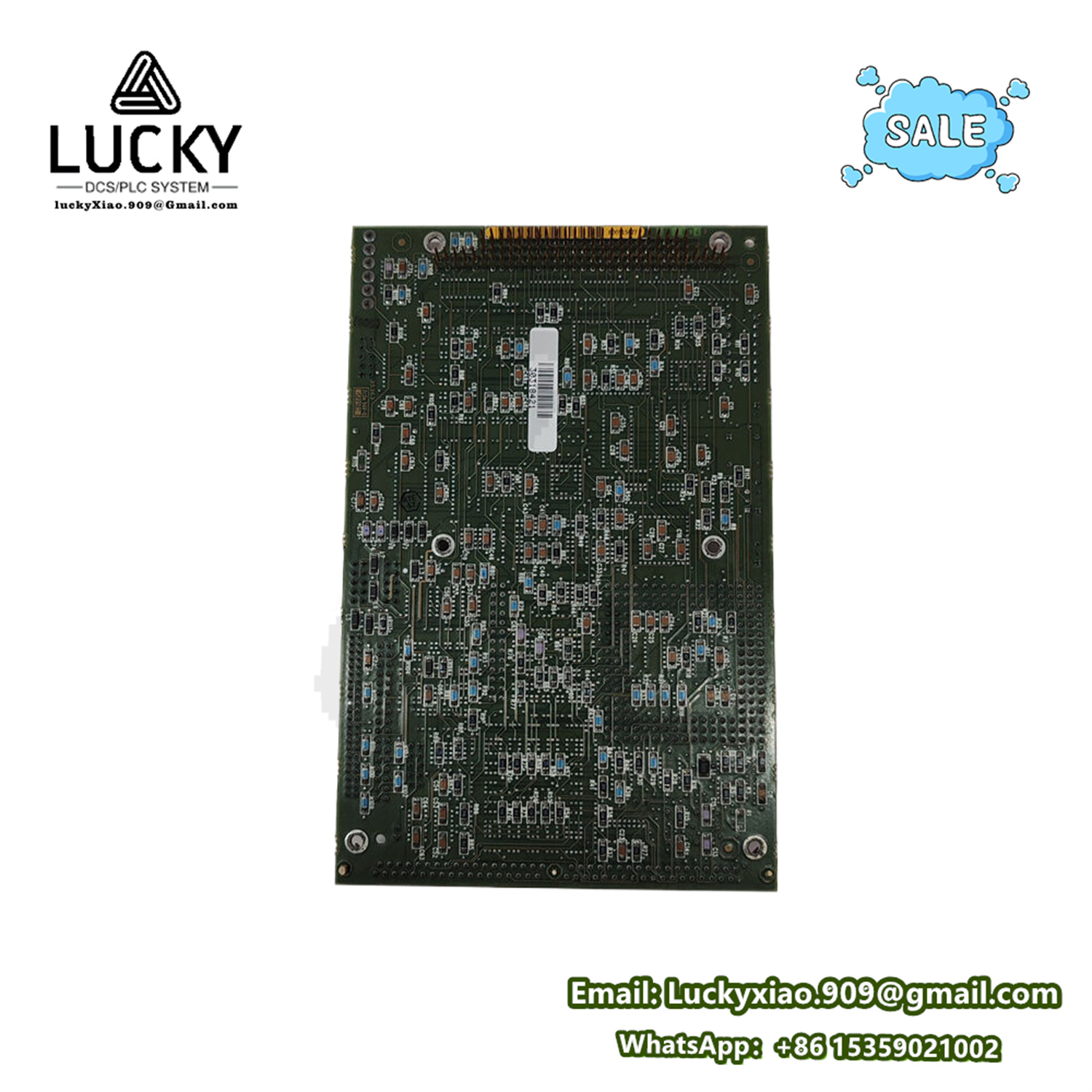

Dimensions

|

324 × 213 × 45 mm (12.8 × 8.4 × 1.8 in)

|

|

Weight

|

2.7 kg (6.0 lbs)

|

Performance Metrics

|

Metric

|

Value

|

|---|---|

|

Firing Angle Range

|

0°–180° (adjustable in 0.1° steps)

|

|

Response Time

|

<500 µs (fault-to-block)

|

|

Zero-Cross Detection

|

±0.5° accuracy

|

|

Max Pulse Freq

|

2 kHz (continuous)

|

Key Applications

- Gas Turbine Starting: Controlled torque application via static starter (LCI).

- Excitation Systems: DC field current regulation during synchronization.

- Industrial Drives: Soft-start control for high-power compressors/pumps.

- Retrofit Projects: Upgrading Mark IV to Mark V starter systems.

⚠️ Critical Integration Notes:

- SCR Pairing: Requires matched thyristor sets (e.g., GE A50P120-04) with ≤0.5V forward drop variance.

- Fiber-Optic Limits: Max 30m cable length (62.5/125 µm OM1).

- Cooling: Forced airflow mandatory (>150 LFM) – derate above 40°C ambient.

- Firmware Constraints: FPGA must match SCR bridge configuration (G6AFB-xx suffix).

- Voltage Hazard: 125V DC present on test points – use CAT III tools.

- Legacy Alert: Obsolete PLCC chips (U17/U18) prone to failure – keep spares.

There are no reviews yet.